推荐厂家

暂无

暂无

留言咨询

留言咨询

银牌8年

银牌8年

400-860-5168转3927

400-860-5168转3927

留言咨询

留言咨询

留言咨询

留言咨询

400-801-8117

400-801-8117

留言咨询

留言咨询

400-860-5168转2630

400-860-5168转2630

留言咨询

留言咨询

400-803-2502

400-803-2502

留言咨询

留言咨询

heller2156MK7回流焊炉是HELLER公司的一款高端产品,其内置热监控功能可以有效提升生产效率;氮气使用量少于100ppm,同时配备Energy Management System,可减少氮气消耗40%以上。该设备使用寿命长、维护成本低,并且采用12英寸宽加热器模块,具有优异的均温性能。在半导体先进封装行业中,稳定并兼容洁净室环境的回流焊工艺对于球固定至关重要。而HELLER的MK7系列回流焊机正好满足这些要求,并且已在北美、韩国、台湾和东南亚等地区广泛应用。[img=,690,387]https://ng1.17img.cn/bbsfiles/images/2023/06/202306130858312664_4672_5802683_3.jpg!w690x387.jpg[/img]Heller公司还为半导体先进封装球固定行业提供了完整的解决方案。他们专门针对该领域开发了一套系统,包括粘接材料、加工设备以及相应技术支持。这使得用户可以更加便捷地实现高质量、高效率以及低成本的生产过程。总之,heller2156MK7回流焊炉是半导体先进封装行业中蕞佳的选择之一。除了其高效、稳定和环保等优点外,HELLER公司还提供完整的技术支持和解决方案,帮助用户更好地完成生产任务。[b]苏州仁恩机电科技有限公司[/b]始终坚持高品质、创新和技术引领的发展战略,致力于为客户提供更好的产品和服务。如果您需要任何heller回流焊的帮助或咨询,请随时联系我们。

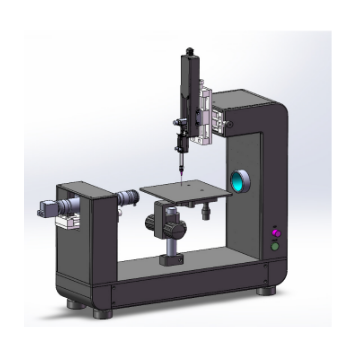

1月3日消息,博纳半导体设备(浙江)有限公司(以下简称「博纳半导体」)获得数千万元A轮融资,资方为宁波梓禾和嘉善经开同芯创业投资,独木资本将为项目的后续融资提供财务顾问服务。资金将用于生产基地建设,技术团队建设以及完善公司管理体系。「博纳半导体」创始人兼CEO刘亮表示,当摩尔定律发展到极致,晶圆也在越做越薄——在先进封装应用中,晶圆厚度一般小于100μm,晶圆减薄技术是封装技术工序中最重要的工艺之一。「博纳半导体」创始人兼CEO刘亮表示,临时键合和解键合流程此前多用日本设备,但日本厂商往往有不平等条约,比如需要采用其指定的材料、为不少额外类目的付费等等,并且交付周期和价格也更长,国产设备相比之下,优势则高下立现。据介绍,目前「博纳半导体」已经推出了临时键合、临时解键合设备、临时解键合清洗一体机在内的三款设备,公司已建设完整的打样试验线,为客户提供一体化,完整工艺段的服务。相比国外设备,「博纳半导体」产品造价是国外同等产品的一半左右。并且,这些机器的零部件中有超过85%为该公司自主研发,更加自主可控,也可配合下游客户的具体需求。目前,「博纳半导体」的商业化进展快速,已经与国内先进封装龙头企业长电科技及关联企业交付数台整机设备、并且实现量产。团队方面,「博纳半导体」创始人兼CEO刘亮有着超过 15 年的先进封装、晶圆制造设备开发经验,团队拥有自主知识产权、全国首创的临时解键合清洗一体机产业化技术。领投方梓禾资本创始人郑昕表示,「博纳半导体」公司产品具备较大的先进性,处于国内领先地位。公司设备相较进口设备具有性价比高、设备重量轻体积小等优势,并符合国家战略发展方向;临时键合/解键合设备在先进封装、化合物半导体、MicroLED等领域均具有较大应用场景;「博纳半导体」发展思路清晰,在围绕晶圆临时键合/解键合工艺进行前后端机台研发,未来发展前景可期。[来源:投资界][align=right][/align]

光学系统校准完整校准的问题我用的是利曼的porfileICP,最近在做光学系统校准完整校准时,光强度比以前低了,并且后面有的峰有波动。我做了了个参考位置校准,也是一样。请问这是为什么?